隨著中國社會老齡化進程加速,養老地產作為融合養老服務與地產開發的新興領域,正逐漸成為市場關注的焦點。本調研從市場規模、政策環境、競爭格局及發展趨勢等方面,對中國養老地產行業進行全面分析。

一、市場規模與需求特征

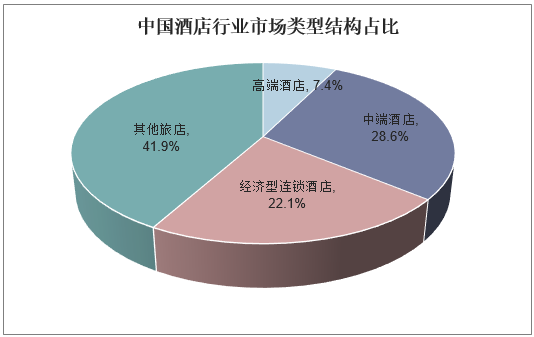

中國養老地產市場潛力巨大。根據國家統計局數據,截至2023年,中國60歲及以上人口已達2.8億,占總人口比例超過19%。預計到2035年,老年人口將突破4億,老齡化率升至30%以上。龐大的老年群體催生了多樣化的養老需求,從基礎居住到醫療護理、文化娛樂、精神慰藉等綜合服務。目前,養老地產主要分為養老社區、養老公寓、康養小鎮等類型,覆蓋高端、中端及普惠不同層次。

二、政策環境與支持措施

近年來,國家層面密集出臺政策鼓勵養老地產發展。例如,《“十四五”國家老齡事業發展和養老服務體系規劃》明確提出支持社會資本參與養老設施建設,優化土地供應和財稅政策。各地方政府也通過補貼、貸款貼息等方式吸引企業投資。行業仍面臨土地性質界定不清、養老設施標準不統一等挑戰,需進一步細化監管框架。

三、競爭格局與主要參與者

養老地產市場參與者多元,包括房地產企業、保險公司、醫療機構等。頭部房企如萬科、保利等依托社區資源開發“養老+地產”模式;保險公司如泰康、平安利用資金優勢布局高端養老社區;專業養老運營商則聚焦服務精細化。目前,市場集中度較低,區域發展不均衡,一線城市和沿海地區較為成熟,中西部地區尚處起步階段。企業競爭核心正從硬件設施轉向服務質量與運營效率。

四、發展趨勢與挑戰

未來,中國養老地產將呈現三大趨勢:一是智慧化融合,物聯網、大數據等技術應用于健康監測和緊急響應;二是醫養結合深化,強化醫療資源嵌入;三是多元化模式創新,如旅居養老、互助養老等。同時,行業也面臨盈利模式不清晰、專業人才短缺、消費者信任度不足等挑戰。企業需通過標準化服務、品牌建設和跨界合作提升競爭力。

中國養老地產行業機遇與挑戰并存。在政策紅利與需求擴張的驅動下,市場有望持續增長,但成功關鍵在于精準定位目標客群、構建可持續商業模式,并堅持以服務為核心的價值導向。